Why Virtual Memory? - to handle shortage of memory - more active process than physical memory can hold - to handle excess memory - 32bit processor could support 64GB of RAM - to support multiprogramming - memory protection - memory sharing Advantages of paging - allocation of memory is easy and cheap - no external fragmentation Disadvantages of paging - mapping table overhead - internal fragmentation

A TLB is part of the chip’s memory-management unit (MMU), and is simply a hardware cache of popular virtual-to-physical address translations. A typical TLB might have 32, 64, or 128 entries.

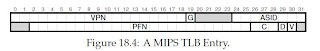

The MIPS R4000 supports a 32-bit address space with 4KB pages. The VPN translates to up to a 24-bit PFN, and hence can support systems with up to 64GB of (physical) main memory (2^24 4KB pages).

- global bit (G), globally-shared page

- address space identifier (ASID)

- Coherence (C) bits, how a page is cached by the hardware

- a valid bit, a valid translation present in the entry.

- a page mask, for multiple page sizes

if the number of pages a program accesses in a short period of time exceeds the number of pages that fit into the TLB, the program will generate a large number of TLB misses, and thus run quite a bit more slowly.

- database management system (a DBMS), which have certain data structures that are both large and randomly-accessed.

Reference:

http://pages.cs.wisc.edu/~remzi/OSFEP/vm-tlbs.pdf

http://cs.nyu.edu/~gottlieb/courses/2000-01-fall/arch/lectures/lecture-23.html

http://www.slideshare.net/vitlic/linux-memory

No comments:

Post a Comment